# ower Doubler Amplifier ADCA3270

75Ω 45 to 1218 MHz

#### **FEATURES**

Drop-in replacement for RFCM3327 and RFCM3328 Total composite power: 73 dBmV High power gain: 25 dB at 1218 MHz **Excellent linearity Very low distortion**

Composite triple beat: -80 dBc typical Composite second-order: -80 dBc typical Carrier to intermodulation noise: 59 dB typical Low noise figure: 3 dB typical at 45 MHz and 4 dB typical at

1218 MHz

**Unconditionally stable**

Configurable current: 350 mA to 480 mA at 24 V

**Temperature monitor**

9-terminal thermally enhanced chip array small outline no lead cavity [LGA\_CAV]

#### **APPLICATIONS**

45 MHz to 1218 MHz community access television (CATV) infrastructure amplifier systems Remote physical layer (PHY) **DOCSIS 3.1 compliant**

#### **GENERAL DESCRIPTION**

The Mini-Circuits' ADCA3270 is a 24 V power doubler, monolithic microwave IC (MMIC) with 25 dB of power gain. The device achieves high RF output up to 73 dBmV composite power under 18 dB tilt conditions by using advanced circuit design techniques with gallium arsenide (GaAs), pseudomorphic high electron transistor (pHEMT), and gallium nitride (GaN) HEMT technologies. The dc current and supply voltage can be adjusted externally for optimum distortion performance vs. power consumption over a range of output levels. The ADCA3270 provides high gain, simplifying the design and manufacturing of DOCSIS 3.1 infrastructure equipment.

The ADCA3270 is packaged in a 9-terminal thermally enhanced chip array small outline no lead cavity [LGA\_CAV] with an industry-standard footprint.

This part was acquired by Mini-Circuits from Analog Devices on April 12, 2024.

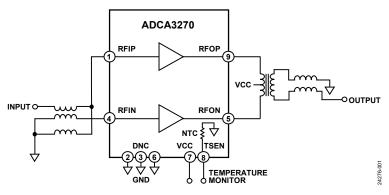

#### **FUNCTIONAL BLOCK DIAGRAM**

# Power Doubler Amplifier ADCA3270

45 to 1218 MHz

## **TABLE OF CONTENTS**

| Features                                    | 1 |

|---------------------------------------------|---|

| Applications                                | 1 |

| General Description                         | 1 |

| Functional Block Diagram                    | 1 |

| Revision History                            | 2 |

| Specifications                              | 3 |

| General Performance                         | 3 |

| Distortion Data (All Digital Channel Plan)  | 3 |

| Distortion Data (Mixed Signal Channel Plan) | 4 |

| Absolute Maximum Ratings                    | 5 |

| Thermal Resistance                          | 5 |

| Electrostatic Discharge (ESD) Ratings       | 5 |

| ESD Caution                                 | 5 |

| Pin Configuration and Function Descriptions | 6 |

| Typical Performance Characteristics              | /      |

|--------------------------------------------------|--------|

| S-Parameters                                     | 7      |

| 9 dB Tilt Performance                            | 8      |

| 18 dB Tilt Performance                           | 9      |

| Theory of Operation                              | 10     |

| Applications Information                         | 11     |

| ADCA3270 Temperature Sense Monitor               | 11     |

| Thermal Considerations                           | 11     |

| Soldering Information and Recommended PCB Land F | attern |

|                                                  | 11     |

| ADCA3270 Bias Current                            | 12     |

| Outline Dimensions                               | 14     |

| Ordonina Cuido                                   | 1.4    |

### **REVISION HISTORY**

4/2024 - Revision A: Transferred from Analog Devices to Mini-Circuits

7/2021 - Revision 0: Initial Version

# Power Doubler Amplifier ADCA3270

45 to 1218 MHz

### **SPECIFICATIONS**

### **GENERAL PERFORMANCE**

Supply voltage ( $V_{CC}$ ) = 24 V, exposed paddle temperature ( $T_{PADDLE}$ ) = 35°C, source impedance ( $Z_s$ ) = load impedance ( $Z_L$ ) = 75  $\Omega$ , and dc current ( $I_{CC}$ ) = 480 mA, unless otherwise noted.

Table 1.

| Parameter                                   | Symbol                  | Min  | Тур  | Max  | Unit | Test Conditions/Comments                                                                            |  |

|---------------------------------------------|-------------------------|------|------|------|------|-----------------------------------------------------------------------------------------------------|--|

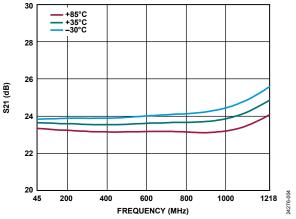

| POWER GAIN                                  | S21                     | 22.0 | 23.6 | 25.0 | dB   | Frequency = 45 MHz, see Figure 4                                                                    |  |

|                                             |                         | 23.0 | 25   | 26.5 | dB   | Frequency = 1218 MHz, see Figure 4                                                                  |  |

| SLOPE STRAIGHT LINE <sup>1</sup>            |                         |      | 2.0  |      | dB   | Frequency = 45 MHz to 1218 MHz                                                                      |  |

| FLATNESS OF FREQUENCY RESPONSE <sup>2</sup> |                         |      | 0.75 |      | dB   | Frequency = 45 MHz to 1218 MHz                                                                      |  |

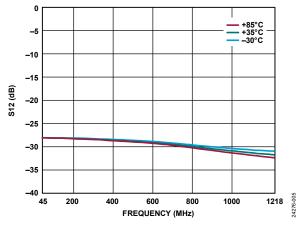

| REVERSE ISOLATION                           | S12                     |      | 28 0 |      | dB   | Frequency = 45 MHz to 1218 MHz, see Figure 5                                                        |  |

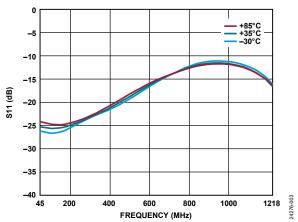

| RETURN LOSS                                 |                         |      |      |      |      | See Figure 3 and Figure 6                                                                           |  |

| Input                                       | S11                     |      | -20  |      | dB   | Frequency = 45 MHz to 320 MHz                                                                       |  |

|                                             |                         |      | -15  |      | dB   | Frequency = 320 MHz to 640 MHz                                                                      |  |

|                                             |                         |      | -12  |      | dB   | Frequency = 640 MHz to 870 MHz                                                                      |  |

|                                             |                         |      | -12  |      | dB   | Frequency = 870 MHz to 1000 MHz                                                                     |  |

|                                             |                         |      | -12  |      | dB   | Frequency = 1000 MHz to 1218 MHz                                                                    |  |

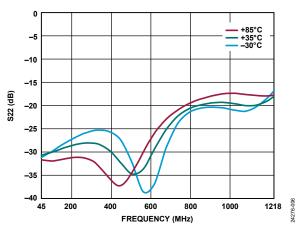

| Output                                      | S22                     |      | -20  |      | dB   | Frequency = 45 MHz to 320 MHz                                                                       |  |

|                                             |                         |      | -20  |      | dB   | Frequency = 320 MHz to 640 MHz                                                                      |  |

|                                             |                         |      | -20  |      | dB   | Frequency = 640 MHz to 870 MHz                                                                      |  |

|                                             |                         |      | -20  |      | dB   | Frequency = 870 MHz to 1000 MHz                                                                     |  |

|                                             |                         |      | -18  |      | dB   | Frequency = 1000 MHz to 1218 MHz                                                                    |  |

| NOISE FIGURE                                |                         |      | 3    |      | dB   | Frequency = 45 MHz                                                                                  |  |

|                                             |                         |      | 4    |      | dB   | Frequency = 1218 MHz                                                                                |  |

| SUPPLY                                      |                         |      |      |      |      |                                                                                                     |  |

| Voltage                                     | V <sub>CC</sub>         | 18   | 24   | 26   | V    | Supply voltage can be adjusted for different applications, see the Applications Information section |  |

| DC Current (Total)                          | I <sub>CC (TOTAL)</sub> | 350  | 480  | 500  | mA   | Can be biased between 350 mA and 480 mA (see the Applications Information section)                  |  |

| RF Input Bias Voltage                       | $V_{BIAS}$              |      | 1.08 |      | ٧    |                                                                                                     |  |

<sup>&</sup>lt;sup>1</sup> Slope straight line is defined as the delta between the gain at the start frequency and the gain at the stop frequency.

#### **DISTORTION DATA (ALL DIGITAL CHANNEL PLAN)**

$V_{CC}$  = 24 V,  $T_{PADDLE}$  = 35°C, and  $Z_S$  =  $Z_L$  = 75  $\Omega$ , unless otherwise noted.

#### Table 2.

| Parameter             | Symbol | Min | Тур | Max | Unit | Test Conditions/Comments                                            |

|-----------------------|--------|-----|-----|-----|------|---------------------------------------------------------------------|

| TOTAL COMPOSITE POWER | ТСР    |     | 73  |     | dBmV | 18 dB tilt, 190 digital (256 QAMs) channels from 57 MHz to 1215 MHz |

|                       |        |     | 73  |     | dBmV | 9 dB tilt, 190 digital (256 QAMs) channels from 57 MHz to 1215 MHz  |

<sup>&</sup>lt;sup>2</sup> Flatness of frequency response is defined as the delta between the gain at any frequency between the start and stop frequencies and a straight line reference drawn between the gain at the start frequency and the gain at the stop frequency.

# Power Doubler Amplifier ADCA3270

75Ω 45 to 1218 MHz

#### **DISTORTION DATA (MIXED SIGNAL CHANNEL PLAN)**

$V_{CC} = 24 \text{ V}$ ,  $T_{FLANGE} = 35^{\circ}\text{C}$ , and  $Z_{S} = Z_{L} = 75 \Omega$ , unless otherwise noted.

#### Table 3.

| Parameter                        | Symbol | Min | Тур | Max | Unit | Test Conditions/Comments                                                                                                                                                                                                                                           |

|----------------------------------|--------|-----|-----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DISTORTION                       |        |     |     |     |      | TCP = 72.4 dBmV, the analog and digital channel plan consists of 18 dB extrapolated tilt, 79 continuous wave channels plus 111 digital channels, a National Television System Committee (NTSC) frequency raster range of 55.25 MHz to 547.25 MHz, and –6 dB offset |

| Composite Triple Beat            | СТВ    |     | -80 |     | dBc  | Defined by the National Cable and Telecommunications Association (NCTA)                                                                                                                                                                                            |

| Composite Second-Order           | CSO    |     | -80 |     | dBc  | Defined by NCTA                                                                                                                                                                                                                                                    |

| Carrier to Intermodulation Noise |        |     | 59  |     | dB   | Defined by American National Standard/Society of Cable Telecommunications Engineers (ANSI/SCTE) 17 (test procedure for carrier to noise)                                                                                                                           |

## Power Doubler Amplifier ADCA3270

45 to 1218 MHz

### ABSOLUTE MAXIMUM RATINGS

Table 4.

| Parameter                                                                            | Rating          |

|--------------------------------------------------------------------------------------|-----------------|

| V <sub>cc</sub>                                                                      |                 |

| DC Supply over Voltage (5 minute)                                                    | 30 V            |

| RF Input Voltage (RFINPUT), Single Tone                                              | 75 dBmV         |

| Temperature                                                                          |                 |

| Operating Range, TPADDLE                                                             | −30°C to +110°C |

| Peak Reflow (Moisture Sensitivity Level (MSL) 3                                      | 260°C           |

| Junction (T <sub>J</sub> ) to Maintain 1 Million Hour<br>Mean Time to Failure (MTTF) | 170°C           |

| Nominal Junction (T <sub>J</sub> )                                                   |                 |

| $T_{PADDLE} = 110^{\circ}C$ , $I_{CC} = 480 \text{ mA}$ , $V_{CC} = 24 \text{ V}$    | 144°C           |

| Storage (T <sub>s</sub> ) Range                                                      | −40°C to +150°C |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JC}$  is the thermal resistance from the operating portion of the PHEMT device to the outside surface of the package closest to the device mounting area (the exposed paddle on the bottom of the case). See the Thermal Considerations section for additional information.

**Table 5. Thermal Resistance**

| Package Type | $\theta_{JC}^{1}$ | Unit |

|--------------|-------------------|------|

| CE-9-2       | 2.9               | °C/W |

$<sup>^1</sup>$  Thermal resistance  $(\theta_{\text{JC}})$  is defined as between the  $T_{\text{PADDLE}}$  and the internal device junction (T<sub>1</sub>).

#### **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

#### **ESD Ratings for ADCA3270**

Table 6. ADCA3270, 6-Terminal LGA\_CAV

| ESD Model | Withstand Threshold (V) | Class            |

|-----------|-------------------------|------------------|

| НВМ       | 500                     | Class 1B, passed |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# Power Doubler Amplifier ADCA3270

75Ω 45 to 1218 MHz

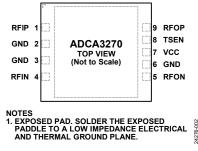

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 7. Pin Function Descriptions**

| 1 4010 7 . 1 | Table 7.1 in 1 and tion 2 configurations |                                                                                                |  |  |  |  |  |

|--------------|------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin No.      | Mnemonic                                 | Description                                                                                    |  |  |  |  |  |

| 1, 4         | RFIP, RFIN                               | RF Differential Inputs.                                                                        |  |  |  |  |  |

| 2, 3, 6      | GND                                      | Ground.                                                                                        |  |  |  |  |  |

| 5, 9         | RFON, RFOP                               | RF Differential Outputs.                                                                       |  |  |  |  |  |

| 7            | VCC                                      | Positive Supply Voltage, 24 V Typical.                                                         |  |  |  |  |  |

| 8            | TSEN                                     | Temperature Sensing Pin.                                                                       |  |  |  |  |  |

|              |                                          | Exposed Pad. Solder the exposed paddle to a low impedance electrical and thermal ground plane. |  |  |  |  |  |

# Power Doubler Amplifier ADCA3270

75Ω 45 to 1218 MHz

### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{CC}$  = 24 V,  $T_{PADDLE}$  = 35°C, and  $Z_S$  =  $Z_L$  = 75  $\Omega$ , unless otherwise noted.

#### **S-PARAMETERS**

Figure 3. S11 vs. Frequency at Various Temperatures

Figure 4. S21 vs. Frequency at Various Temperatures

Figure 5. S12 vs. Frequency at Various Temperatures

Figure 6. S22 vs. Frequency at Various Temperatures

# Power Doubler Amplifier ADCA3270

45 to 1218 MHz 75Ω

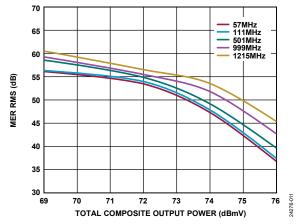

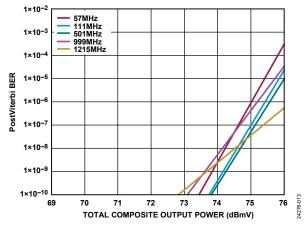

#### 9 dB TILT PERFORMANCE

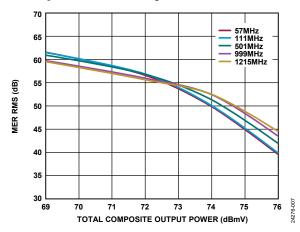

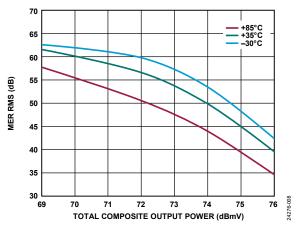

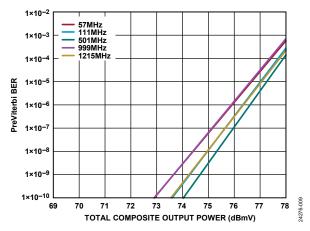

9 dB extrapolated tilt and 190 digital channels (QAM256, ITU-T J.83, Annex B).

Figure 7. MER RMS vs. Total Composite Output Power at Various Frequencies, 35℃, 9 dB Tilt

Figure 8. MER RMS vs. Total Composite Output Power at Various Temperatures, 57 MHz, 9 dB Tilt

Figure 9. PreViterbi BER vs. Total Composite Output Power at Various Frequencies, 35°C, 9 dB Tilt

Figure 10. PreViterbi BER vs. Total Composite Output Power at Various Temperatures, 57 MHz, 9 dB Tilt

# Power Doubler Amplifier ADCA3270

45 to 1218 MHz 75Ω

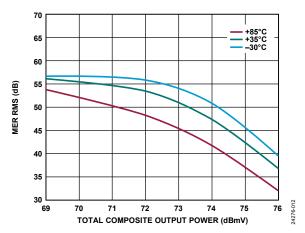

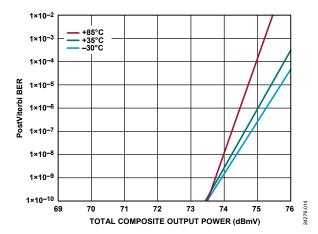

#### **18 dB TILT PERFORMANCE**

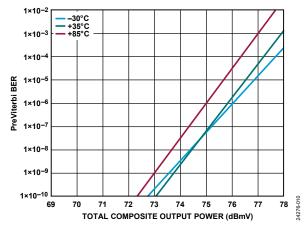

18 dB extrapolated tilt and 190 digital channels (QAM256, ITU-T J.83, Annex B).

Figure 11. MER RMS vs. Total Composite Output Power at Various Frequencies, 35℃, 18 dB Tilt

Figure 12. MER RMS vs. Total Composite Output Power at Various Temperatures, 57 MHz, 18 dB Tilt

Figure 13. PostViterbi BER vs. Total Composite Output Power at Various Frequencies, 35°C, 18 dB Tilt

Figure 14. PostViterbi BER vs. Total Composite Output Power at Various Temperatures, 57 MHz, 18 dB Tilt

# ower Doubler Amplifier ADCA3270

75Ω 45 to 1218 MHz

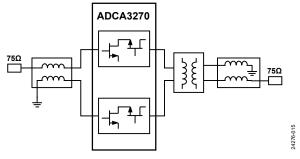

### THEORY OF OPERATION

The ADCA3270 is a balanced amplifier packaged in a LGA\_CAV. The application circuit interfaces the ADCA3270 to a 75  $\Omega$  input and output matched impedance consistent with a matched module designed for CATV applications. The ADCA3270 uses cascode field effect transistor (FET) feedback amplifiers in a Class A push pull configuration. The bottom half of the cascode stages are implemented in a single die, linear FET process that minimizes parasitics, thereby enabling higher gain. The top devices in the cascodes are implemented using a linear GaN process that is able to swing high RF voltages. The frequency of operation is from 45 MHz to 1218 MHz.

The ADCA3270 is unconditionally stable for robust operation in systems targeting DOCSIS 3.1 and legacy DOCSIS standards.

Figure 15. Simplified Schematic

# Power Doubler Amplifier ADCA3270

75Ω 45 to 1218 MHz

### APPLICATIONS INFORMATION

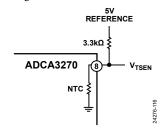

#### **ADCA3270 TEMPERATURE SENSE MONITOR**

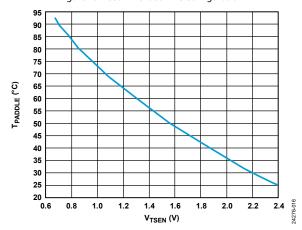

The ADCA3270 has an internally mounted, negative temperature coefficient (NTC) thermistor that, when used as the bottom of a resistive voltage divider, provides an output voltage that is correlated to the ground temperature at the TPADDLE of the LGA\_CAV package. When configured as shown in Figure 16, the typical relationship between  $V_{\mbox{\tiny TSEN}}$  and  $T_{\mbox{\tiny PADDLE}}$  results in what is shown in Figure 17.

Figure 16. Recommended NTC Configuration

Figure 17. TPADDLE VS. VTSEN

#### THERMAL CONSIDERATIONS

The ADCA3270 is packaged in a thermally efficient, 9-terminal chip array small outline no lead cavity [LGA\_CAV]. The thermal resistance from  $\theta_{IC}$  is 2.9°C/W, where the case is defined by the exposed paddle on the bottom of the package. For the best thermal performance, it is recommended that as many thermal vias as possible be added under the exposed paddle of the LGA\_CAV package. For optimal performance, it is recommended that these vias be filled with a paste that has high thermal conductivity. It is also recommended that the array of

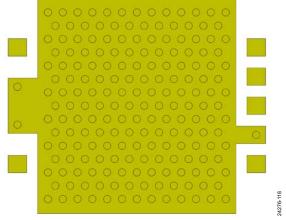

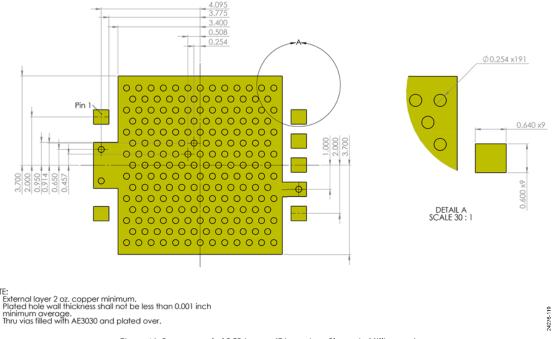

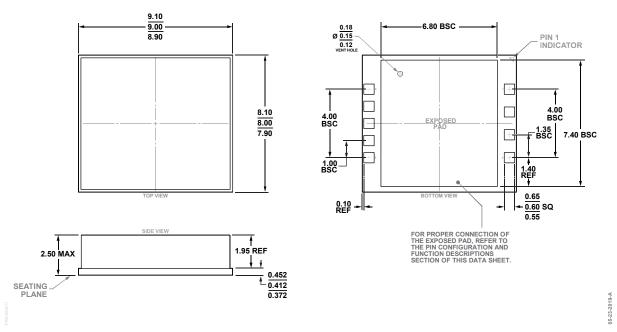

### SOLDERING INFORMATION AND RECOMMENDED **PCB LAND PATTERN**

Figure 18 shows the recommended land pattern for the ADCA3270. To minimize thermal impedance, the exposed paddle on the 9.00 mm × 8.00 mm LGA\_CAV is soldered to a ground plane along with Pin 2, Pin 3, and Pin 6. To improve thermal dissipation, 188 thermal vias are arranged in an array under the exposed paddle. The array consists of alternating rows of 13 vias and 12 vias, maximizing the number of vias within the area. The area under the paddle is also tied to ground on the bottom layer of the PCB. If multiple ground layers exist, tie these layers together by the vias. The external layer of the PCB must be a minimum of 2 oz. copper. The minimum average plated hole wall thickness of the vias must not be less than 0.001 inch, and it is recommended that the vias be filled with a conductive paste, such as Tatsuta AE3030, and plated over. The full recommended PCB footprint design is shown in Figure 19.

Figure 18. Recommended Land Pattern

For further information on optimizing the thermal performance while using the ADCA3270, refer to the AN-1604 Application Note, Thermal Management Calculations for RF Amplifiers in LFCSP and Flange Packages.

# Power Doubler Amplifier ADCA3270

45 to 1218 MHz

Figure 19. Recommended PCB Layout (Dimensions Shown in Millimeters)

#### **ADCA3270 BIAS CURRENT**

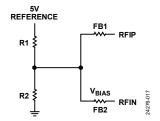

The ADCA3270 employs a versatile circuit design, allowing system designers to configure the supply voltage at the VCC connection (Pin 7) and the bias control voltage (VBIAS) at the RFIP (Pin 1) and RFIN (Pin 4) connections to optimize the power dissipation in any given application. It is recommended that the I<sub>CC</sub> be controlled by employing a precision 5 V reference and a resistor divider (R1 and R2) to set ICC as illustrated in Figure 20. The voltage is connected to each input through a ferrite bead (FB1 and FB2). The dc output of the balun used to feed the RF into the power amplifier must be blocked using a capacitor.

Figure 20. Setting the Bias Control Voltage

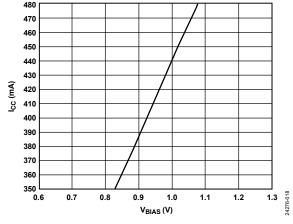

Figure 21 provides the typical transfer function of  $I_{CC}$  to  $V_{BIAS}$ , which allows the user to adjust I<sub>CC</sub> from 380 mA to 480 mA.

Figure 21. Icc vs. VBIAS

# Power Doubler Amplifier ADCA3270

45 to 1218 MHz 75Ω

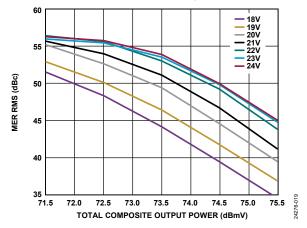

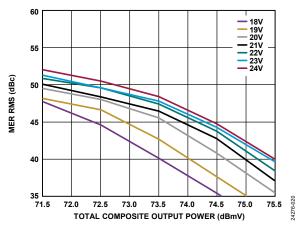

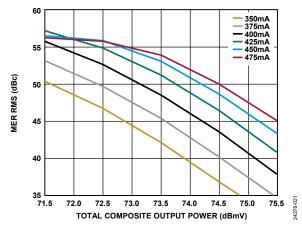

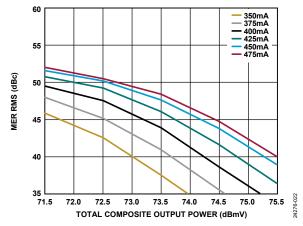

Figure 22 and Figure 23 illustrates the MER performance tradeoff for different supply voltage configurations. Figure 24 and Figure 25 illustrates the modulation error ratio performance trade-off for different bias current configurations.

Figure 22. MER RMS vs. Total Composite Output Power,  $I_{CC} = 475 \text{ mA}$ ,  $V_{CC} = 18 \text{ V to } 24 \text{ V}, 1 \text{ V Steps}, 9 \text{ dB Tilt}$

Figure 23. MER RMS vs. Total Composite Output Power,  $I_{CC} = 475 \text{ mA}$ ,  $V_{CC} = 18 \text{ V to } 24 \text{ V}, 1 \text{ V Steps}, 22 \text{ dB Tilt}$

Figure 24. MER RMS vs. Total Composite Output Power,  $V_{CC} = 24 V$ , 25 mA Steps from 350 mA to 475 mA, 9 dB Tilt

Figure 25. MER RMS vs. Total Composite Output Power,  $V_{CC} = 24 V$ , 25 mA Steps from 350 mA to 475 mA, 22 dB Tilt

# Power Doubler Amplifier ADCA3270

45 to 1218 MHz 75Ω

### **OUTLINE DIMENSIONS**

Figure 26. 9-Terminal Chip Array Small Outline No Lead Cavity [LGA\_CAV]  $9.00\,\mathrm{mm} \times 8.00\,\mathrm{mm}$  Body and  $2.50\,\mathrm{mm}$  Package Height (CE-9-2) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                          | Package Option |

|--------------------|-------------------|--------------------------------------------------------------|----------------|

| ADCA3270ACEZ       | −30°C to +110°C   | 9-Terminal Chip Array Small Outline No Lead Cavity [LGA_CAV] | CE-9-2         |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

- A. Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document.

- Electrical specifications and performance data contained in this specification document are based on Mini-Circuit's applicable established test performance criteria and measurement instructions

- The parts covered by this specification document are subject to Mini-Circuits standard limited warranty and terms and conditions (collectively, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the standard terms and the exclusive rights and remedies thereunder, please visit Mini-Circuits' website at www.minicircuits.com/terms/viewterm.html

- D. Analog Devices and the ADI words and logos are trademarks of Analog Devices, Inc. (or its subsidiaries) in the U.S. and/or elsewhere. All rights reserved.